## AN-1034 Sequencer for 3 Power Rails

Author: Saif Abu Baker Date: March 26, 2014

#### Introduction

Many applications require a controlled cycle during power-up and power-down.

The GreenPAK2 controls the starting time of each of 3 power rails, and the shutdown time.

### **Description**

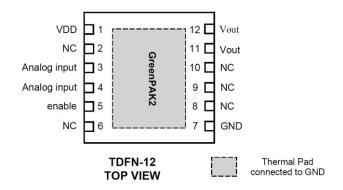

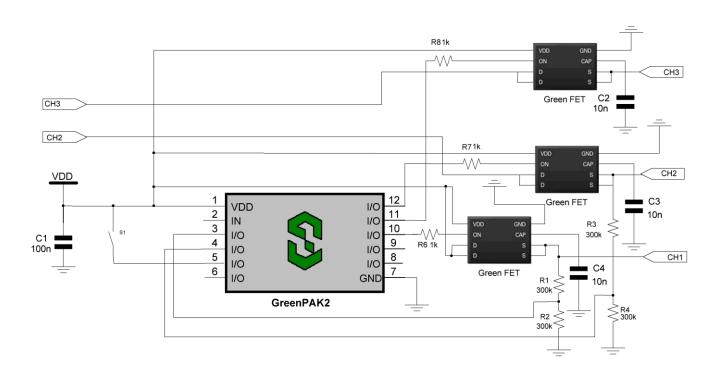

Pins 3, 4 each have an internal  $300 \text{K}\Omega$  resistor, and  $300 \text{K}\Omega$  external resistors in the schematic to make a voltage divider at the analog inputs to the analog comparators. The circuit then determines if the previous channel got started up based on the voltage, and whether to start the next channel. (outputs at pins 10, 11, 12).

Figure 1. Pin configuration

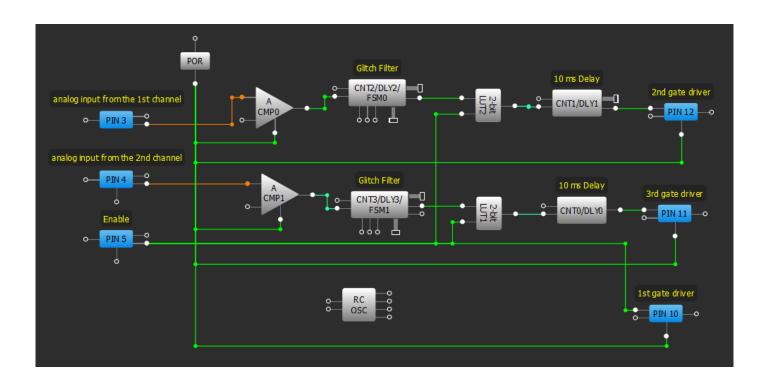

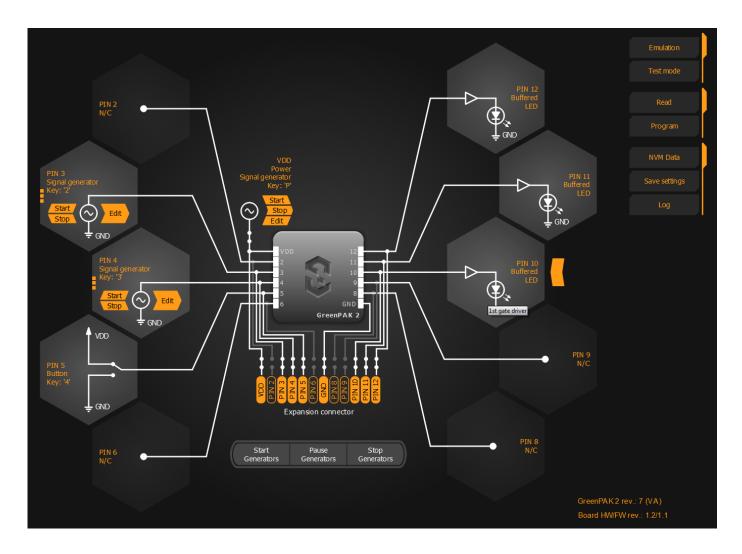

Figure 2. Design connections in GreenPAK2 Designer

www.silego.com Page 1 of 7

The enable switch starts the circuit by pin 5, and drives the 1st channel signal through pin 10, and on to a loadswitch (SLG59M301V).

The loadswitches used in this design are Silego GreenFETs. They have integrated MOSFETs, short/thermal protection, and slew rate control based on capacitors C2, C3, C4.

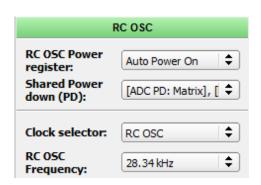

In this example, the RC OSC is set to be always ON by choosing the option Force Power On, and it will provide a 28.34 KHz clock frequency.

Figure 3. RC OSC properties

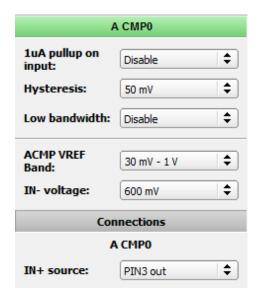

The ACMP0 and ACMP1 properties are set as 600mV reference voltage to make delay equal to the input ramp time reaching the 600mV x 2 (because of the 300K external resistor voltage dividers). Also, the Hysteresis is set to 50 mV to reduce effect of input glitches.

POR is used to remove any ACMP glitch during powerup. ACMP0 is configured to auto power detect.

Figure 4. POR properties

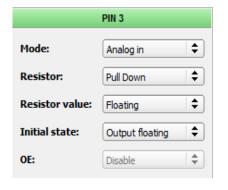

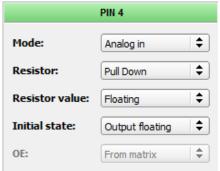

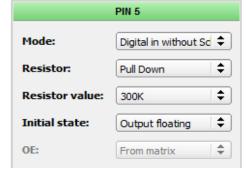

Pins 3, 4 are configured as analog inputs with floating pull down resistor. Pin 5 is configured as digital input with 300k pull down resistor (figure 7)

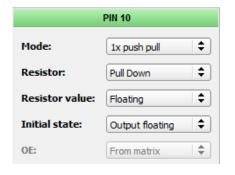

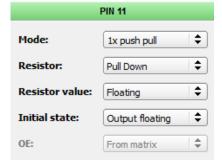

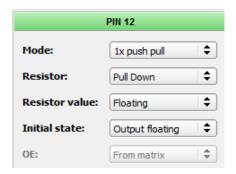

The pins 10, 11, 12 are configured as 1X push pull with floating pull down resistor (figure 8).

| Symbol            | Parameter                       | Min. | Тур.    | Max. | Unit |

|-------------------|---------------------------------|------|---------|------|------|

| $V_{THD}$         | ACMP0 Voltage Threshold         | 575  | -       | 625  | mV   |

| $V_{THD}$         | ACMP1 Voltage Threshold         | 575  | -       | 625  | mV   |

| V <sub>AIR</sub>  | ACMP Analog Input Voltage Range | 0    | -       | 1000 | mV   |

| T <sub>DLY0</sub> | DLY0 Time Delay                 | -    | 10.0917 | -    | ms   |

| T <sub>DLY1</sub> | DLY1 Time Delay                 | -    | 10.0917 | -    | ms   |

| T <sub>DLY2</sub> | DLY2 Time Delay                 | -    | 0.1059  | -    | ms   |

| T <sub>DLY3</sub> | DLY3 Time Delay                 | -    | 0.1059  | -    | ms   |

**Table 1. Design Main Electrical Characteristics**

www.silego.com Page 2 of 7

Figure 5. A CMP0 properties

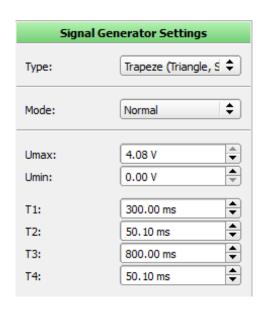

**Figure 6. Signal Generator Settings**

Figure 7. PIN 3, PIN 4 and PIN 5 properties

Figure 8. PIN 10, PIN 11 and PIN 12 properties

www.silego.com Page 3 of 7

**Figure 9. Typical Application Circuit**

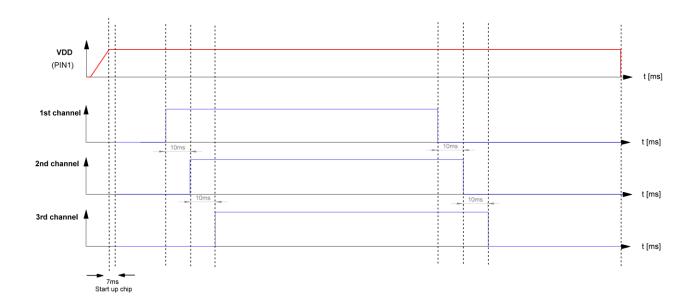

Figure 10. Timing Diagram

www.silego.com Page 4 of 7

Figure 11. GreenPAK2 Emulation Tool

### Conclusion

A GreenPAK2 was configured to control the power sequence of several power rails. This is useful for power management or system control considerations.

www.silego.com Page 5 of 7

### **About the Author**

Name: Saif Abu Baker

Background: Saif Abu Baker graduated from Yarmouk University in 2013, studying at the Department

of Electrical Power Engineering. Presently he is working with Configurable Mixed Signal

ICs (CMICs) and their application notes and power supplies designing.

Contact: appnotes@silego.com

www.silego.com Page 6 of 7

## **Document History**

Document Title: Sequencer for 3 Power Rails

Document Number: AN-1034

| Revision | Orig. of Change | Submission Date | Description of Change |

|----------|-----------------|-----------------|-----------------------|

| А        | Saif Abu Baker  | 3/26/2014       | New application note  |

#### **Worldwide Sales and Design Support**

Silego Technology maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at **Silego Locations**.

#### **About Silego Technology**

Silego Technology, Inc. is a fabless semiconductor company headquartered in Santa Clara, California, with operations in Taiwan, and additional design/technology centers in China, Korea and Ukraine.

**Silego Technology Inc.** 1715 Wyatt Drive Santa Clara, CA 95054

Phone

: 408-327-8800

Fax

: 408-988-3800

Website

: www.silego.com

www.silego.com Page 7 of 7